# Advanced CISC Implementations: Pentium 4

Krste Asanovic

Laboratory for Computer Science

M.I.T.

http://www.csg.lcs.mit.edu/6.823

# **Intel Pentium Pro (1995)**

Krste Asanovio May 7, 2001 6.823, L22--2

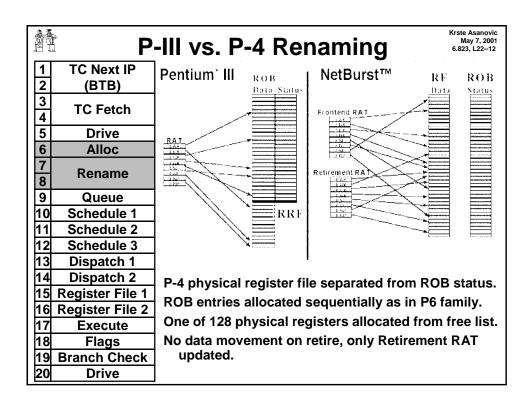

- During decode, translate complex x86 instructions into RISC-like micro-operations (uops)

- e.g., "R ← R op Mem" translates into

load T, Mem # Load from Mem into temp reg  $R \leftarrow R$  op T # Operate using value in temp

- Execute uops using speculative out-of-order superscalar engine with register renaming

- Pentium Pro family architecture (P6 family) used on Pentium-II and Pentium-III processors

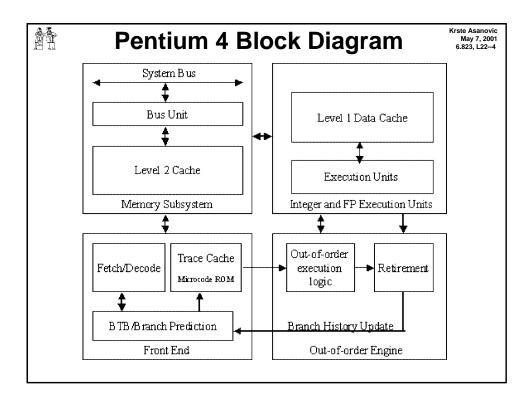

# Intel Pentium 4 (2000)

Krste Asanovic May 7, 2001 6.823, L22--3

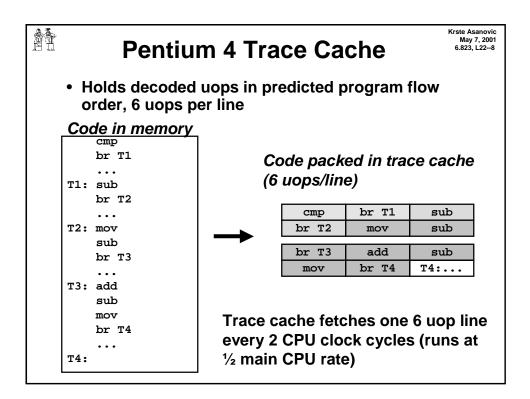

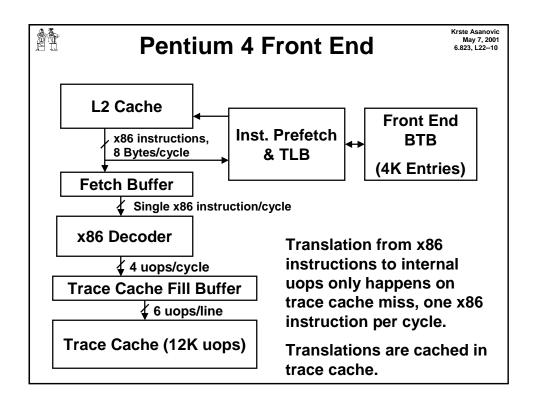

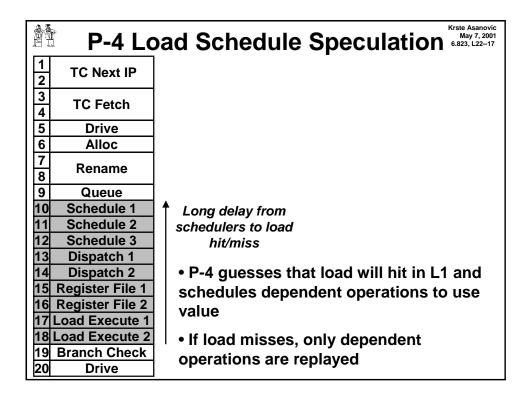

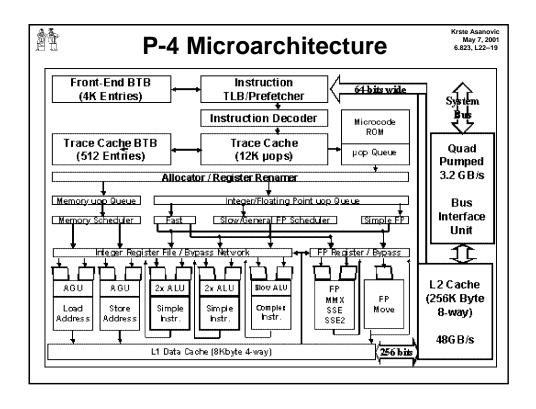

- · Deeper pipelines than P6 family

- about half as many levels of logic per pipeline stage as P6

- Trace cache holds decoded uops

- only has a single x86->uop decoder

- Decreased latency in same process technology

- aggressive circuit design

- new microarchitectural tricks

This lecture contains figures and data taken from: "The microarchitecture of the Pentium 4 processor", Intel Technology Journal, Q1, 2001

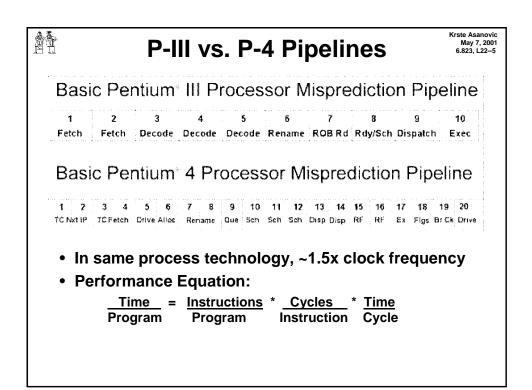

### **Deep Pipeline Design**

Krste Asanovic May 7, 2001 6.823, L22--7

#### **Greater potential throughput but:**

- Clock uncertainty and latch delays eat into cycle time budget

- doubling pipeline depth gives less than twice frequency improvement

- Clock load and power increases

- more latches running at higher frequencies

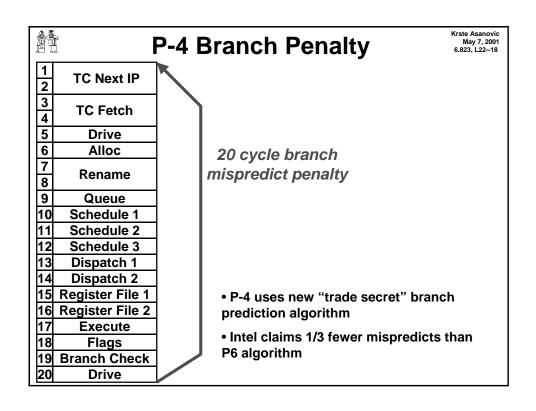

- More complicated microarchitecture needed to cover long branch mispredict penalties and cache miss penalties

- from Little's Law, need more instructions in flight to cover longer latencies → larger reorder buffers

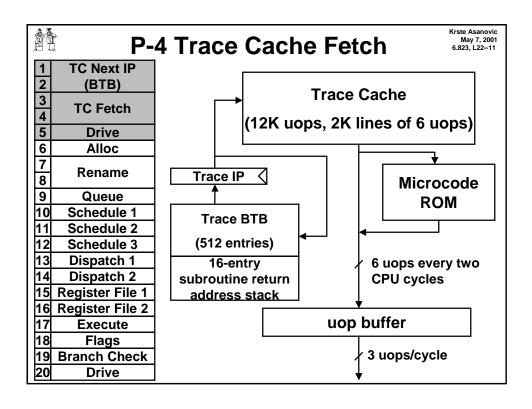

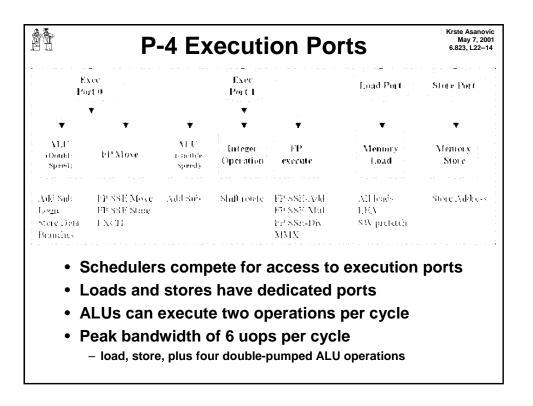

- P-4 has three major clock domains

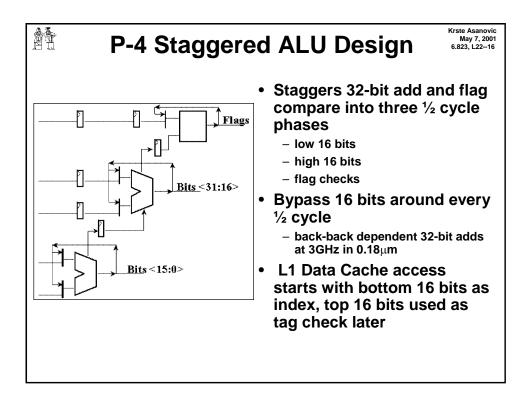

- Double pumped ALU (3 GHz), small critical area at highest speed

- Main CPU pipeline (1.5 GHz)

- Trace cache (0.75 GHz), save power

### **Trace Cache Advantages**

Krste Asanovic May 7, 2001 6.823, L22--9

- Removes x86 decode from branch mispredict penalty

- Parallel x86 decoder took 2.5 cycles in P6, would be 5 cycles in P-4 design

- Allows higher fetch bandwidth fetch for correctly predicted taken branches

- P6 had one cycle bubble for correctly predicted taken branches

- P-4 can fetch a branch and its target in same cycle

- Saves energy

- x86 decoder only powered up on trace cache refill

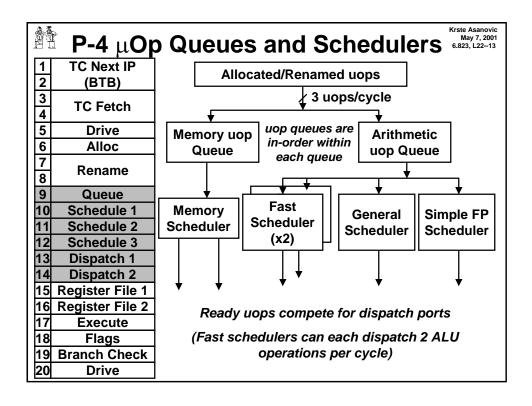

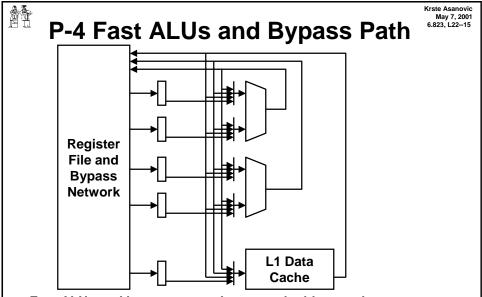

- · Fast ALUs and bypass network runs at double speed

- All "non-essential" circuit paths handled out of loop to reduce circuit loading (shifts, mults/divs, branches, flag/ops)

- · Other bypassing takes multiple clock cycles

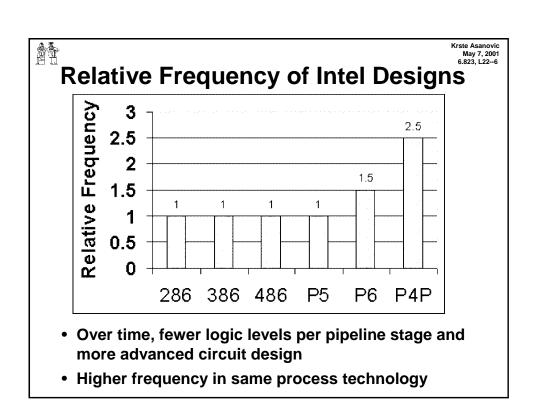

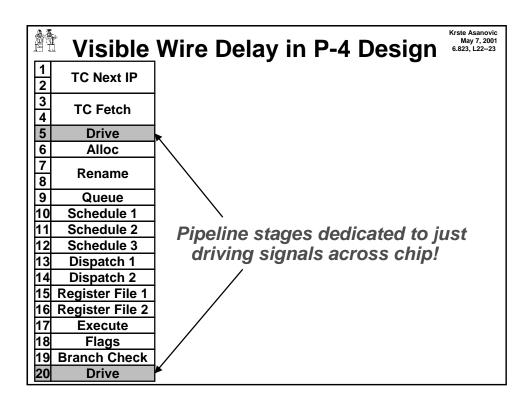

## **Scaling of Wire Delay**

Krste Asanovic May 7, 2001 6.823, L22--22

- Over time, transistors are getting relatively faster than long wires

- wire resistance growing dramatically with shrinking width and height

- capacitance roughly fixed for constant length wire

- RC delays of fixed length wire rising

- Chips are getting bigger

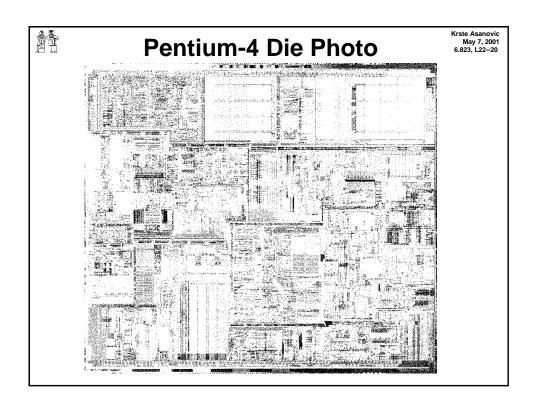

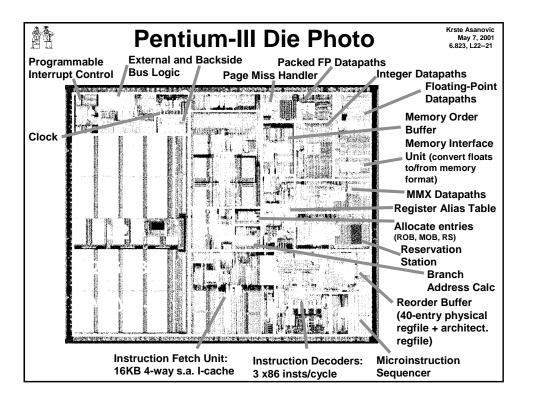

- P-4 >2x size of P-III

- Clock frequency rising faster than transistor speed

- deeper pipelines, fewer logic gates per cycle

- more advanced circuit designs (each gate goes faster)

- ⇒ Takes multiple cycles for signal to cross chip

Krste Asanovic May 7, 2001 6.823, L22--24

### **Instruction Set Translation**

- · Convert a target ISA into a host machine's ISA

- Pentium Pro (P6 family)

- translation in hardware after instruction fetch

- Pentium-4 family

- translation in hardware at level 1 instruction cache refill

- Transmeta Crusoe

- translation in software using "Code Morphing"